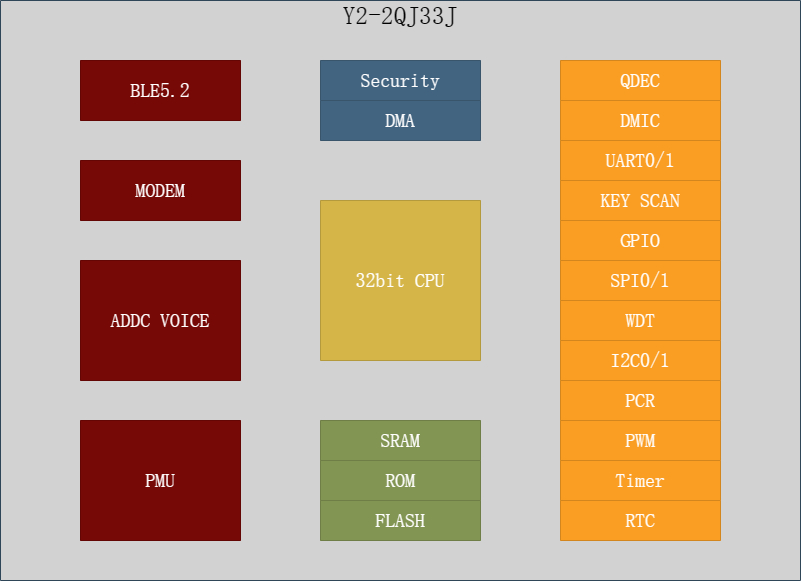

• Low power 32bit CPU • Memory: Optional 128 KB - 8 MB Flash 64 KB SRAM data maintain sleep mode 4-channel instruction cache with 8KB of cache RAM 96KB ROM 256bit efuse • Support DMIC/AMIC microphone function • Support 6-channel 32-bit timers and watchdog timers • Support for real-time counters (RTC) • Support for power, clock and reset controls

Y2-2QJ33J

Function Description

The Y2-2QJ33J is a system-on-chip (SoC) for BLE 5.2 applications. It is powered by a 32bit CPU and possesses 64K Retention SRAM, supports a maximum of 8M Flash, 96KB ROM, and 256bit eFuse. Integrated ultra-low power, high performance multi - mode RF transceiver.

Size Package: QFN32(4mm x 4mm)

Operating temperature:

40 ˚ C ~ + 85 ˚ C (consumer)

40 ˚ C ~ + 105 ˚ C (industrial grade)

Y2-2QJ33J supports BLE based security architectures, applications, and OTA online upgrades. In addition, serial peripheral IO and integrated application IP also enable customers to develop their own products with minimal BOM cost. Y2-2QJ33J can be widely used in smart wearable, smart home, smart lighting, Bluetooth remote control, electronic price tag, Bluetooth beacon, medical health, smart building, smart industry and other industries and products.

Product performance

System characteristics

BLE features

•High speed data throughput: Support BLE 2 MBPS Support data length extension function The highest data throughput 1.6 megabits per second (DLE + 2 Mbps)

Interface features

•22 general IO pin •Off/dormancy mode GPIO state reserves •All pins can set serial interface and editable IO MUX function mapping; •All pins can be set to awaken state •All pins can raise the interrupt •Three QDEC decoder •6-channel PWM •2-channel PDM/IIC/SPI/UART •DMA 4-channel

System Block Diagram