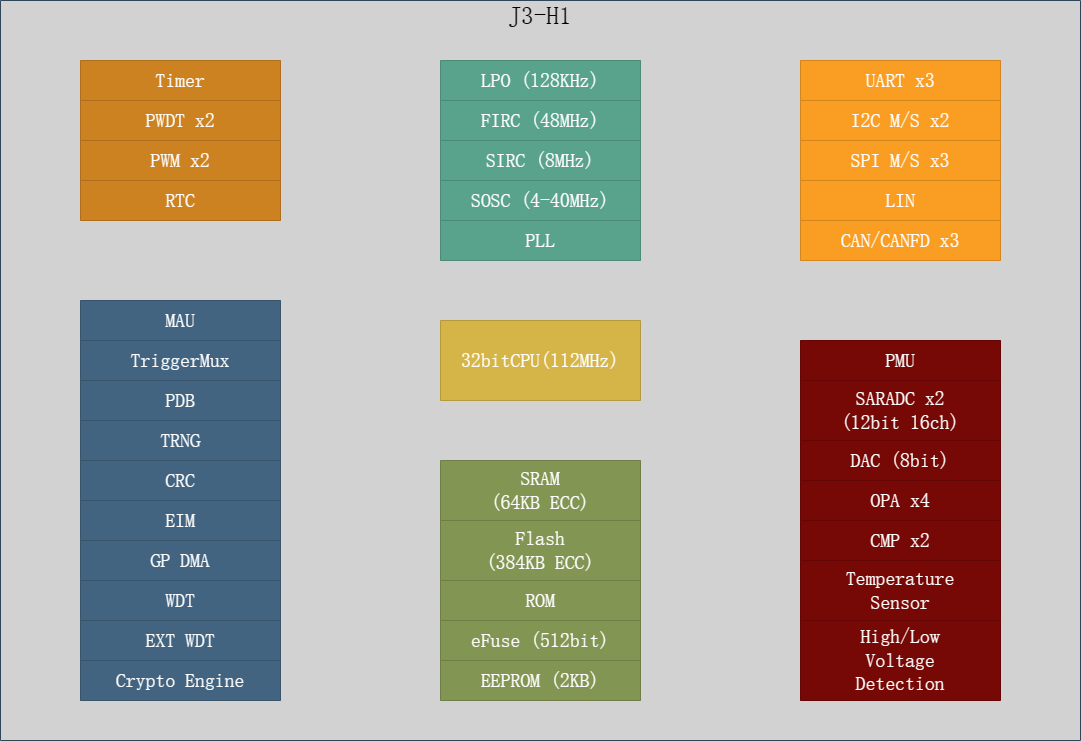

•32bit CPU •Support 32bit single-cycle multipliers •384KBs embedded Flash (ECC) support •Support 64KBs SRAM (ECC) •Feature a motor control algorithm accelerator (MAU)

J3-H1

Function Description

Highly scalable platform

32bit CPU architecture, good ecological environment

Large capacity Flash/RAM, rich peripheral resources for platform expansion

Ultra-high reliability

ISO26262 and AEC-Q100 Grade 1 certified

Support -40°C~125°C

15-year design life, >15 years supply chain warranty

High-cost performance

Better price/performance ratio for the same performance/resources

Product performance

System Resources

Peripheral resources

•3-channel CAN-FD, CAN 2.0B compatible •3-channel UART, 1-channel supports UART LIN multiplexing •3-channel SPI (master-slave mode supported) •2-channel I2C (master-slave mode support) •2-channel hardware LIN •2 x 8-channel complementary pulse width modulation (PWM) timers •1 x 4-channel periodic interrupt timer •2 pulse width timers (PWDT) •1 real time clock (RTC)

Simulation

•2 x 12bit AdC, 1Msps, supporting 16-channel •1个8bit DAC •2 x analog comparators with built-in 8bit Dac •4x operational amplifier •1x temperature sensor, ±0.5℃

Package

•LOFP 48 ( 7mmx7mm ) •LQFP 64 ( 10mmx10mm ) •LQFP 100( 14mmx14mm ) •LQFP 144( 20mmx20mm ) •LQFP 176( 24mmx24mm )

System Block Diagram